DRAIN

SOURCE

SDURCE SEE PACKAGE OUTLINE FOR MARKING CODE

GATE

- PERFORMANCE (1.8 GHz)

- ◆ 34.5 dBm Output Power (P<sub>1dB</sub>)

- ◆ 12 dB Power Gain (G<sub>1dB</sub>)

- ♦ 45 dBm Output IP3

- ♦ 8V Operation

- 50% Power-Added Efficiency

- Evaluation Boards Available

- Design Data Available on Website

- Suitable for applications to 5 GHz

# DESCRIPTION AND APPLICATIONS

Typical applications include drivers or output stages in PCS/Cellular base station transmitter amplifiers, as well as other power applications in WLL/WLAN amplifiers.

| Parameter                                                          | Symbol            | Test Conditions                                             | Min  | Тур  | Max  | Units |  |  |  |  |  |

|--------------------------------------------------------------------|-------------------|-------------------------------------------------------------|------|------|------|-------|--|--|--|--|--|

| <b>RF SPECIFICATIONS MEASURED AT</b> $f = 1.8$ GHz USING CW SIGNAL |                   |                                                             |      |      |      |       |  |  |  |  |  |

| Power at 1dB Gain Compression                                      | $P_{1dB}$         | $V_{DS} = 8V; I_{DQ} = 700 \text{ mA}$                      | 33.5 | 34.5 |      | dBm   |  |  |  |  |  |

|                                                                    |                   | $\Gamma_{\rm S}$ and $\Gamma_{\rm L}$ tuned for Optimum IP3 |      |      |      |       |  |  |  |  |  |

| Power Gain at dB Gain Compression                                  | G <sub>1dB</sub>  | $V_{DS} = 8V; I_{DQ} = 700 \text{ mA}$                      | 10.5 | 12   |      |       |  |  |  |  |  |

|                                                                    |                   | $\Gamma_{\rm S}$ and $\Gamma_{\rm L}$ tuned for Optimum IP3 |      |      |      |       |  |  |  |  |  |

| Maximum Stable Gain                                                | MSG               | $V_{DS} = 8V; I_{DQ} = 700 \text{ mA}$                      |      | 18   |      | dB    |  |  |  |  |  |

| $S_{21}/S_{12}$                                                    |                   | $P_{IN} = 0 dBm, 50\Omega$ system                           |      |      |      |       |  |  |  |  |  |

| Power-Added Efficiency                                             | PAE               | $V_{DS} = 8V; I_{DQ} = 700 \text{ mA}$                      |      | 50   |      | %     |  |  |  |  |  |

| at 1dB Gain Compression                                            |                   | $\Gamma_{\rm S}$ and $\Gamma_{\rm L}$ tuned for Optimum IP3 |      |      |      |       |  |  |  |  |  |

| 3 <sup>rd</sup> -Order Intermodulation Distortion                  | IM3               | $V_{DS} = 8V; I_{DQ} = 700 \text{ mA}$                      |      |      |      |       |  |  |  |  |  |

| $\Gamma_{\text{S}}$ and $\Gamma_{\text{L}}$ tuned for Optimum IP3  |                   | $P_{OUT} = 23 \text{ dBm}$ (single-tone level)              |      | -46  |      | dBc   |  |  |  |  |  |

| Saturated Drain-Source Current                                     | I <sub>DSS</sub>  | $V_{DS} = 1.3 V; V_{GS} = 0 V$                              | 1.9  | 2.3  | 2.65 | mA    |  |  |  |  |  |

| Maximum Drain-Source Current                                       | I <sub>MAX</sub>  | $V_{DS} = 1.3 \text{ V}; V_{GS} \cong +1 \text{ V}$         |      | 3.6  |      | mA    |  |  |  |  |  |

| Transconductance                                                   | G <sub>M</sub>    | $V_{DS} = 1.3 \text{ V}; V_{GS} = 0 \text{ V}$              |      | 2.4  |      | mS    |  |  |  |  |  |

| Gate-Source Leakage Current                                        | I <sub>GSO</sub>  | $V_{GS} = -3 V$                                             |      | 70   | 170  | μΑ    |  |  |  |  |  |

| Pinch-Off Voltage                                                  | $ V_P $           | $V_{DS} = 1.3 \text{ V}; I_{DS} = 8 \text{ mA}$             | 0.7  | 0.9  | 1.4  | V     |  |  |  |  |  |

| Gate-Source Breakdown Voltage                                      | V <sub>BDGS</sub> | $I_{GS} = 8 \text{ mA}$                                     | 6    | 10   |      | V     |  |  |  |  |  |

| Gate-Drain Breakdown Voltage                                       | V <sub>BDGD</sub> | $I_{GD} = 8 \text{ mA}$                                     | 20   | 22   |      | V     |  |  |  |  |  |

| Thermal Resistivity (channel-to-case)                              | $\Theta_{\rm CC}$ | See Note on following page                                  |      | 16   |      | °C/W  |  |  |  |  |  |

# • ELECTRICAL SPECIFICATIONS AT 22°C

# RECOMMENDED OPERATING BIAS CONDITIONS

Drain-Source Voltage:From 5V to 8VQuiescent Current:From 400 mA to 750 mA

# ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Parameter                                       | Symbol           | <b>Test Conditions</b>          | Min | Max              | Units |

|-------------------------------------------------|------------------|---------------------------------|-----|------------------|-------|

| Drain-Source Voltage                            | V <sub>DS</sub>  | $-3V < V_{GS} < +0V$            |     | 12               | V     |

| Gate-Source Voltage                             | V <sub>GS</sub>  | $0V < V_{DS} < +8V$             |     | -3               | V     |

| Drain-Source Current                            | I <sub>DS</sub>  | For $V_{DS} > 2V$               |     | I <sub>DSS</sub> | mA    |

| Gate Current                                    | I <sub>G</sub>   | Forward / Reverse current       |     | +20/-20          | mA    |

| RF Input Power <sup>2</sup>                     | P <sub>IN</sub>  | Under any acceptable bias state |     | 575              | mW    |

| Channel Operating Temperature                   | T <sub>CH</sub>  | Under any acceptable bias state |     | 175              | °C    |

| Storage Temperature                             | T <sub>STG</sub> | Non-Operating Storage           | -40 | 150              | °C    |

| Total Power Dissipation                         | P <sub>TOT</sub> | See De-Rating Note below        |     | 9.0              | W     |

| Gain Compression                                | Comp.            | Under any bias conditions       |     | 5                | dB    |

| Simultaneous Combination of Limits <sup>3</sup> |                  | 2 or more Max. Limits           |     | 80               | %     |

${}^{1}T_{Ambient} = 22^{\circ}C$  unless otherwise noted  ${}^{2}Max$ . RF Input Limit must be further limited if input VSWR > 2.5:1  ${}^{3}Users$  should avoid exceeding 80% of 2 or more Limits simultaneously

#### Notes:

• Operating conditions that exceed the Absolute Maximum Ratings will result in permanent damage to the device.

• Total Power Dissipation defined as:  $P_{TOT} \equiv (P_{DC} + P_{IN}) - P_{OUT}$ , where:

P<sub>DC</sub>: DC Bias Power

P<sub>IN</sub>: RF Input Power P<sub>OUT</sub>: RF Output Power

F<sub>OUT</sub>. KF Output Fower

Total Power Dissipation to be de-rated as follows above 22°C:

$P_{TOT} = 9.0 - (0.0625 \text{W/}^{\circ}\text{C}) \times T_{PACK}$

where  $T_{PACK}$  = source tab lead temperature above 22 °C

(coefficient of de-rating formula is the Thermal Conductivity)

Example: For a 55°C source lead temperature:  $P_{TOT} = 9.0 - (0.0625 \text{ x} (55 - 22)) = 6.94 \text{W}$

- For optimum heatsinking, metal-filled through (Source) via holes should be used directly below the central metallized ground pad on the bottom of the package.

- *Note on Thermal Resistivity:* The nominal value of 16°C/W is measured with the package mounted on a large heatsink with thermal compound to ensure adequate (unsoldered) contact. The package temperature is referred to the Source leads.

# HANDLING PRECAUTIONS

To avoid damage to the devices care should be exercised during handling. Proper Electrostatic Discharge (ESD) precautions should be observed at all stages of storage, handling, assembly, and testing. This product has be tested to Class 1A (> 250V but < 500V) using JESD22 A114, Human Body Model, and to Class A, (< 200V) using JESD22 A115, Machine Model.

### BIASING GUIDELINES

- Active bias circuits provide good performance stabilization over variations of operating temperature, but require a larger number of components compared to self-bias or dual-biased. Such circuits should include provisions to ensure that Gate bias is applied before Drain bias, otherwise the pHEMT may be induced to self-oscillate. Contact your Sales Representative for additional information.

- Dual-bias circuits are relatively simple to implement, but will require a regulated negative voltage supply for depletion-mode devices such as the FPD1000AS.

- > Self-biased circuits employ an RF-bypassed Source resistor to provide the negative Gate-Source bias voltage, and such circuits provide some temperature stabilization for the device. A nominal value for circuit development is  $3.25 \Omega$  for the recommended 200mA operating point.

- The recommended 200mA bias point is nominally a Class AB mode. A small amount of RF gain expansion prior to the onset of compression is normal for this operating point.

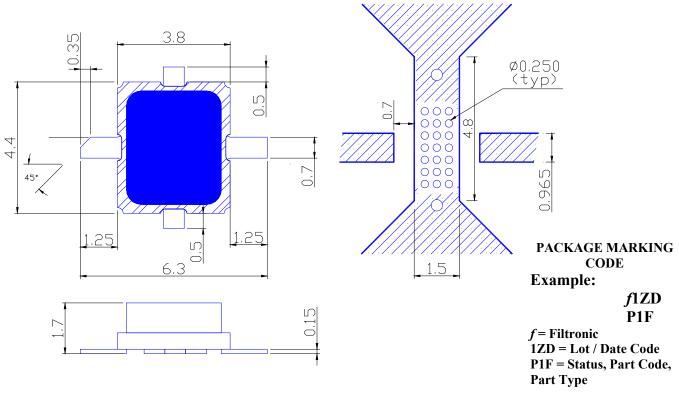

# • PACKAGE OUTLINE AND RECOMMENDED PC BOARD LAYOUT (dimensions in millimeters – mm)

All information and specifications subject to change without nonce.